### AVTECH ELECTROSYSTEMS LTD.

NANOSECOND WAVEFORM ELECTRONICS ENGINEERING . MANUFACTURING

P.O. BOX 265 OGDENSBURG NEW YORK 13669 (315) 472-5270 BOX 5120 STN. "F"

OTTAWA, ONTARIO

CANADA K2C 3H4

(613) 226-5772

TELEX 053-4591

INSTRUCTIONS

MODEL AVK-V-C PULSE GENERATOR

S.N.:

### WARRANTY

Avtech Electrosystems Ltd. warrants products of manufacture to be free from defects in material workmanship under conditions of normal use. If, within one year after delivery to the original owner, and after prepaid return by the original owner, this Avtech product is found to be defective, Avtech shall at its option repair or replace said defective item. This warranty does not apply to units which have been dissembled, modified or subjected to conditions exceeding the applicable specifications or ratings. This warranty is the extent of the obligation or liability assumed by Avtech with respect to this product and no other warranty or guarantee is either expressed or implied.

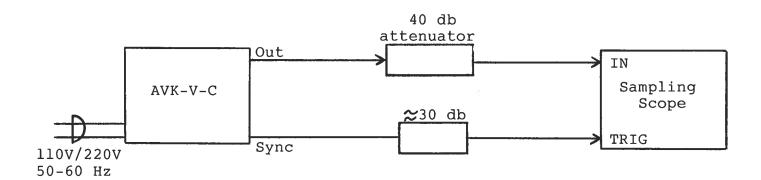

# Fig. 1 PULSE GENERATOR TEST ARRANGEMENT

#### Notes:

- 1) The bandwidth capability of components and instruments used to display the pulse generator output signal (attenuators, cables, connectors, etc.) should exceed ten gigahertz.

- The use of 40 db attenuator at the sampling scope vertical input channel will insure a peak input signal to the sampling scope of less than one volt.

- The sync output channel provides TTL level signals. To avoid overdriving the TRIG input channel of some sampling scopes, a 30 db attenuator should be placed at the input to the sampling scope trigger channel.

- 4) To obtain a stable output display the PRF control on the front panel should be set mid-range while the rear PRF RANGE switch may be in either range. The TRIG toggle switch should be in the INT position. The DELAY controls and the scope triggering controls are then adjusted to obtain a stable output. The scope may then be used to set the desired PRF by rotating the PRF control.

- 5) The output pulse width is controlled by means of the front panel one turn PW control. The control should initially be set maximum clockwise and the pulse width adjusted using an oscilloscope.

- 6) To DC offset the output pulse connect a DC power supply set to required DC offset value to the back panel terminals marked O.S. The maximum attainable DC offset voltage is ±50 volts (option).

- 7) An external clock may be used to control the output PRF of the AVK unit by setting the front panel TRIG toggle switch in the EXT position and applying a 0.2 usec (approx.) TTL level pulse to the TRIG BNC connector input. For operation in this mode, the scope time base must also be triggered by the external clock rather than from the SYNC output.

- 8) For units with the dual output polarity option (-PN) a positive output pulse is obtained at the OUT P SMA connector. To obtain a negative output pulse, the OUT P port is connected to the IN N port via a short length of miniature 50 ohm coaxial cable. A negative output pulse is then obtained at the OUT N port.

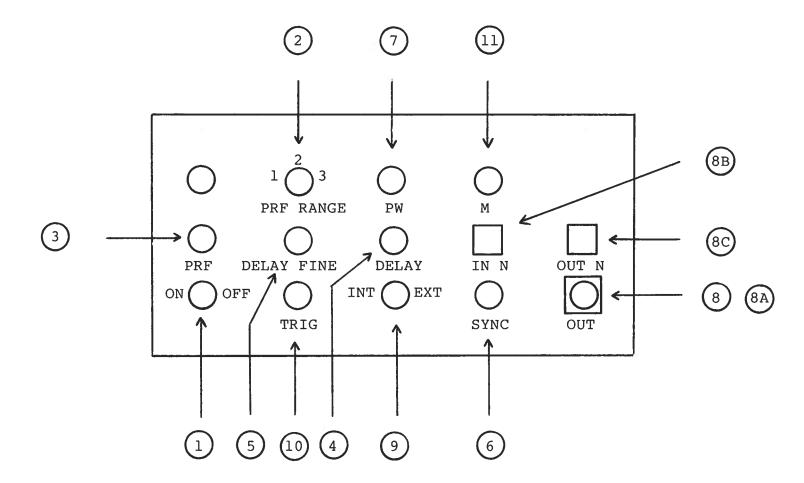

# FRONT PANEL CONTROLS

- (1) ON-OFF Switch. Applies basic prime power to all stages.

- (2) PRF Control. The PRF range switch in 1 position, PRF

- (3) control will vary PRF from 0.05 KHz to about 0.5 KHz. With PRF RANGE switch in 2 position, varies PRF from about 0.5 KHz to about 5 KHz. With the PRF range switch in the 3 position, varies PRF from about 5 KHz to 50 KHz. The operating PRF should be set using a sampling scope.

- (4) <u>DELAY Control</u>. Controls the relative delay between the reference output pulse provided at the SYNC output (6) the main output (8). This delay is variable over the range of 0 to at least 500 nsec.

- (5) <u>DELAY FINE Control</u>. This control varies <u>DELAY</u> but is about 5 times less sensitive than the main <u>DELAY</u> control.

- (6) SYNC Output. This output precedes the main output (8) and is used to trigger the sampling scope time base. The output is a TTL level 100 nsec (approx.) pulse capable of driving a fifty ohm load.

- (7) <u>PW Control</u>. A one turn control which varies the output pulse width from 2 to 50 nsec.

- (8) <u>OUT Connector</u>. SMA connector provides output to a fifty ohm load.

- (8A) <u>OUT P</u>. For units with dual output polarity option, provides positive output pulse.

- (8B) IN N. OUT N. For dual polarity option units connect OUT

- (8C) P to IN N port to obtain negative output pulse at OUT N port.

- (9) EXT-INT Control. With this toggle switch in the INT position, the PRF of the AVK unit is controlled via an internal clock which in turn is controlled by the PRF controls. With the toggle switch in the EXT position, the AVK unit requires a 0.2 usec TTL level pulse applied at the TRIG input in order to trigger the output stages. In addition, in this mode, the scope time base must be triggered by the external trigger source.

- (10) TRIG Input. The external trigger signal is applied at this input when the EXT-INT toggle switch is in the EXT position.

- (11) MONITOR OUT M. Provides an attenuated (x10) coincident replica of the main positive pulse to fifty ohms (option).

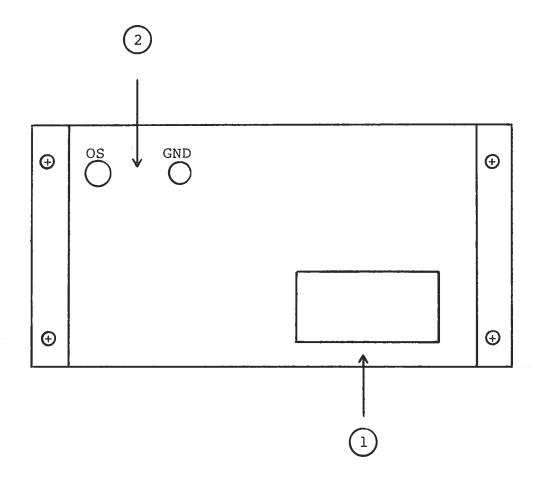

# BACK PANEL CONTROLS

- (1) <u>FUSED CONNECTOR, VOLTAGE SELECTOR</u>. The detachable power cord is connected at this point. In addition, the removable cord is adjusted to select the desired input operating voltage. The unit also contains the main power fuse.

- (2) <u>DC OFFSET Input</u>. To DC offset the output pulse, connect a DC power supply set to the desired offset value to these terminals. The maximum allowable DC offset voltage is ±50 volts (option).

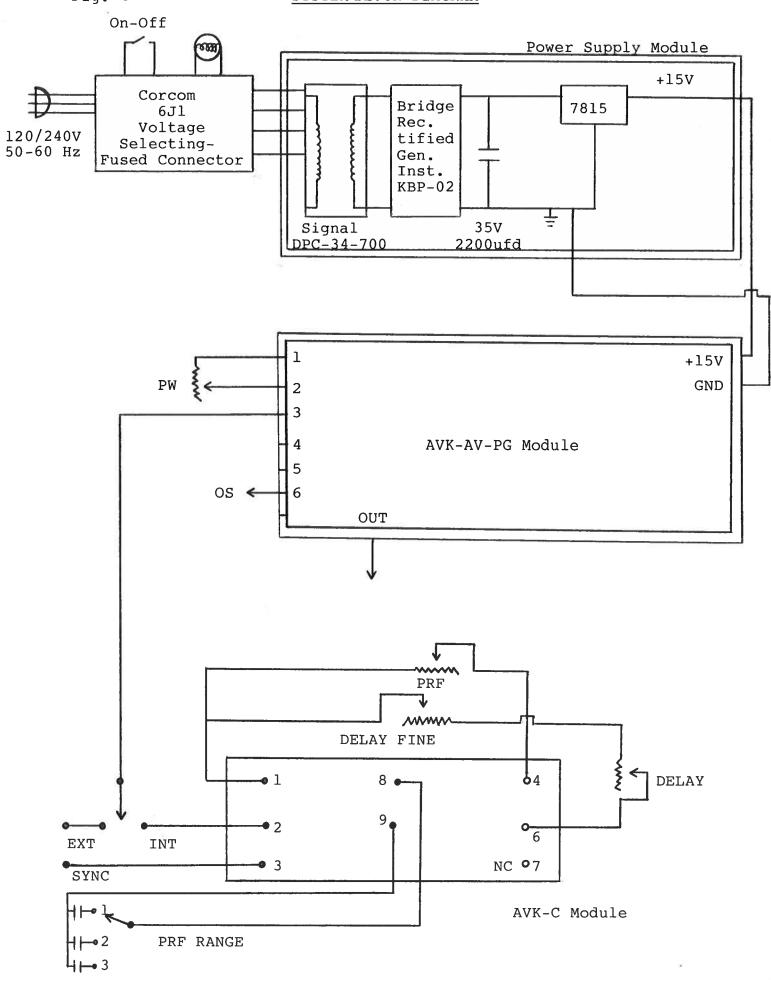

### SYSTEM DESCRIPTION AND REPAIR PROCEDURE

The AVK-V-C consists of a pulse generator module (AVK-V-PG), a clock module AVK-C and a power supply board which supplies +15 volts (600 mA max) to the pulse generator module. In the event that the unit malfuctions, remove the four Phillips screws on the back of the unit. The top cover may then be slid off. Measure the voltage at the +15 V pin of the PG If this voltage is substantially less than +15 module. volts, unsolder the line connecting the power supply and PG modules and connect 50 ohm 10 W load to the PS output. The voltage across this load should be about +15 V DC. If this voltage is substantially less than 15 volts the PS module is defective and should be repaired or replaced. If the voltage across the resistor is near 15 volts, then the PG module should be replaced or repaired. The sealed PG module must be returned to Avtech for repair (or replacement). The clock module provides a 0.1 usec TTL level trigger pulse at pin 2 to trigger the PG module and a 0.1 usec TTL level synch pulse at pin 3 to trigger the sampling scope display device. The output at pin 3 precedes the output at pin 2 by almost 0 to 100 nsec depending on the DELAY control setting. The clock module is powered by +5.8 V supplied by the PG module (from pin 1 to pin 1). With the INT-EXT switch in the EXT position, the clock module is disconnected from the PG module. The clock module is functioning properly if:

- a) 0.1 usec TTL level outputs are observed at pins 2 and 3.

- b) The PRF of the outputs can be varied over the range of 0.05 KHz to 50 KHz using the PRF and PRF RANGE controls.

- c) The relative delay between the pin 2 and 3 outputs can be varied by at least 500 nsec by the DELAY control.

The sealed clock module must be returned to Avtech for repair or replacement if the above conditions are not observed.

And the Military bears of the control of the contro

kændt be mynedn eras skultur bogst til som tyr þe

he can distribute un compensation of the control of

THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY OF THE PROPERTY O