## AVTECH ELECTROSYSTEMS LTD.

NANOSECOND WAVEFORM ELECTRONICS ENGINEERING - MANUFACTURING

P.O. BOX 265 OGDENSBURG NEW YORK 13669 (315) 472-5270 BOX 5120 STN. "F" OTTAWA, ONTARIO CANADA K2C 3H4 (613) 226-5772 TELEX 053-4591

INSTRUCTIONS

MODEL AVMN-3A-P-EA-EW-E0-M1 PULSE GENERATOR

S.N.:

## WARRANTY

Avtech Electrosystems Ltd. warrants products of its manufacture to be free from defects in material and workmanship under conditions of normal use. If, within one year after delivery to the original owner, and after prepaid return by the original owner, this Avtech product is found to be defective, Avtech shall at its option repair or replace said defective item. This warranty does not apply to units which have been dissembled, modified or subjected to conditions exceeding the applicable specifications or ratings. This warranty is the extent of the obligation or liability assumed by Avtech with respect to this product and no other warranty or guarantee is either expressed or implied.

Notes:

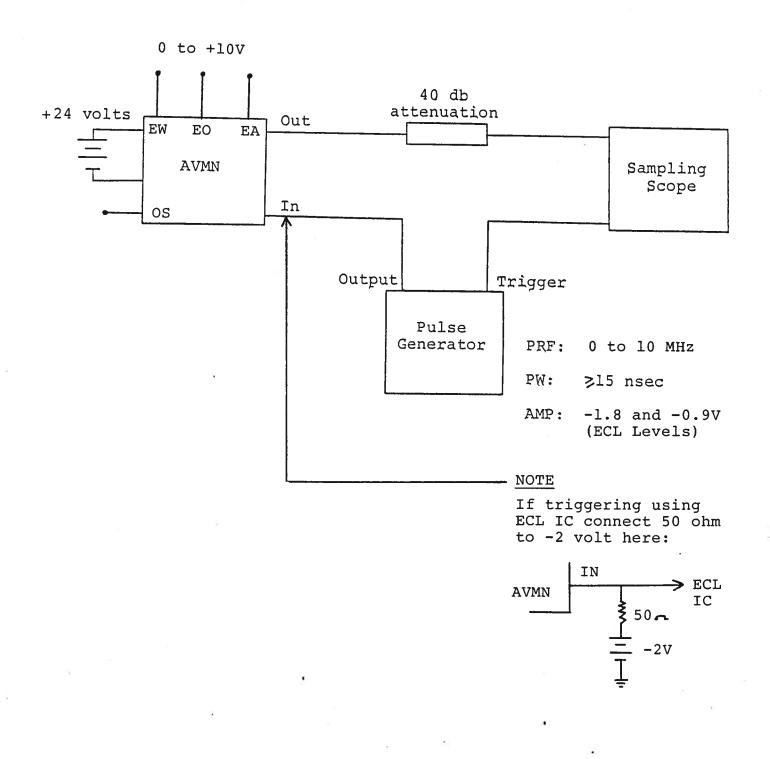

- The bandwidth capability of components and instruments used to display the pulse generator output signal (attenuators, cables, connectors, etc.) should exceed one gigahertz.

- 2) The use of 40 db attenuator will insure a peak input signal to the sampling scope of less than one volt.

- 3) In general, the source pulse generator trigger delay control should be set in the 0.1 to 1.0 usec range.\*

- 4) The AVMN requires an ECL trigger signal (-0.9 and -1.8 volts). If triggered directly from an ECL IC, the input to the AVMN should be shunted by 50 ohms terminated in -2 volts.

- 5) The input trigger pulse width should be greater than 15 nsec and less than one half of the pulse repetition frequency period. The unit triggers on the leading edge of the input trigger signal.

- 6) <u>WARNING</u>: Model AVMN may fail if triggered at a PRF greater than 10.0 MHz.

- 7) The output pulse width and amplitude are each controlled by 0 to +10 volts applied to the EW and EA solder terminals ( $R_{IN} \ge 10K$ ).

- 8) The output DC offset is controlled by 0 to +10 volts applied to the EO solder terminal when the EO switch is in the ON position. The output offset is -5 volts when OV is applied and increases to +5 volts when +10 volts is applied. When the EO switch is in the OFF position, the internally generated offset is inactive but a DC offset can be applied by connecting a desired potential to the rear panel OS solder terminal.

11:27.87

- 13 The demonstrative carbon of a structure of the contract of the contract

- 3 The assist of PTMS Alustical are write presented a peak instituenced of the simple in Security of Feel Phase States.

- 13 In questal, the stance null to denie the point site of initial distance in an and the stance in the set frame.

- Als the events of a constraint of the gravity of the second se

- 21 the troub trouged by second manual method then the mean and issonables toget have delivering reactivities programme and transformer transformer a the transform on the two to the transform.

- The second part and the second state about both the second rest 100. Extended when a spectrum the observed and show recommended from a second state.

- a) Represent the ansate of vertical beam with a set and a monthmet Santhar EG to be an the croat when the EU switch of its the the bit should be a show the contract with a set of all to end the set of the flat with a set of set its and the coll of generations when the Bur with a set of set its and the coll of the set of the bit beam of the Bur with a set of set its and the set of the coll of the set of the set of the set of the set of the flat of the set of the Bur with a set of the rest part of the set of the set of the set of the flat set of the rest part of the set of the set of the set of the set of the rest part of the set of the set of the set of the set of the rest part of the set of the set of the set of the set of the rest part of the set of the set of the set of the set of the rest part of the set of the set of the set of the set of the rest part of the set of the rest part of the set of the rest part of the set of the rest part of the set of the rest part of the set of the