### AVTECH ELECTROSYSTEMS LTD.

NANOSECOND WAVEFORM ELECTRONICS SINCE 1975

P.O. BOX 265 OGDENSBURG, NY U.S.A. 13669-0265 TEL: (315) 472-5270 FAX: (613) 226-2802 TEL: 1-800-265-6681 FAX: 1-800-561-1970

e-mail: info@avtechpulse.com http://www.avtechpulse.com P.O. BOX 5120 STN. F OTTAWA, ONTARIO CANADA K2C 3H4 TEL: (613) 226-5772 FAX: (613) 226-2802

## **INSTRUCTIONS**

### **MODEL AVO-8B-C PULSE GENERATOR**

S.N.:

### **WARRANTY**

Avtech Electrosystems Ltd. warrants products of its manufacture to be free from defects in material and workmanship under conditions of normal use. If, within one year after delivery to the original owner, and after prepaid return by the original owner, this Avtech product is found to be defective, Avtech shall at its option repair or replace said defective item. This warranty does not apply to units which have been dissembled, modified or subjected to conditions exceeding the applicable specifications or ratings. This warranty is the extent of the obligation assumed by Avtech with respect to this product and no other warranty or guarantee is either expressed or implied.

### TECHNICAL SUPPORT

Phone: 613-226-5772 or 1-800-265-6681 Fax: 613-226-2802 or 1-800-561-1970

E-mail: info@avtechpulse.com

World Wide Web: http://www.avtechpulse.com

# **TABLE OF CONTENTS**

| WARRANTY                                 | 2  |

|------------------------------------------|----|

| TABLE OF CONTENTS                        | 3  |

| FIG. 1: PULSE GENERATOR TEST ARRANGEMENT | 4  |

| GENERAL OPERATING INSTRUCTIONS           | 5  |

| Fig. 2: FRONT PANEL CONTROLS             | 9  |

| FRONT PANEL CONTROLS1                    | 0  |

| FIG. 3: BACK PANEL CONTROLS1             | 12 |

| BACK PANEL CONTROLS1                     | 3  |

| AVO-8-C BLOCK DIAGRAM1                   | 14 |

| FIG. 4: SYSTEM BLOCK DIAGRAM1            | 15 |

| PERFORMANCE CHECK SHEET1                 | 16 |

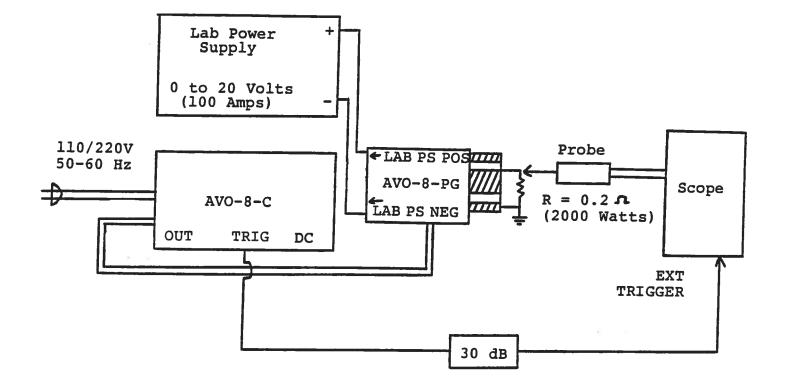

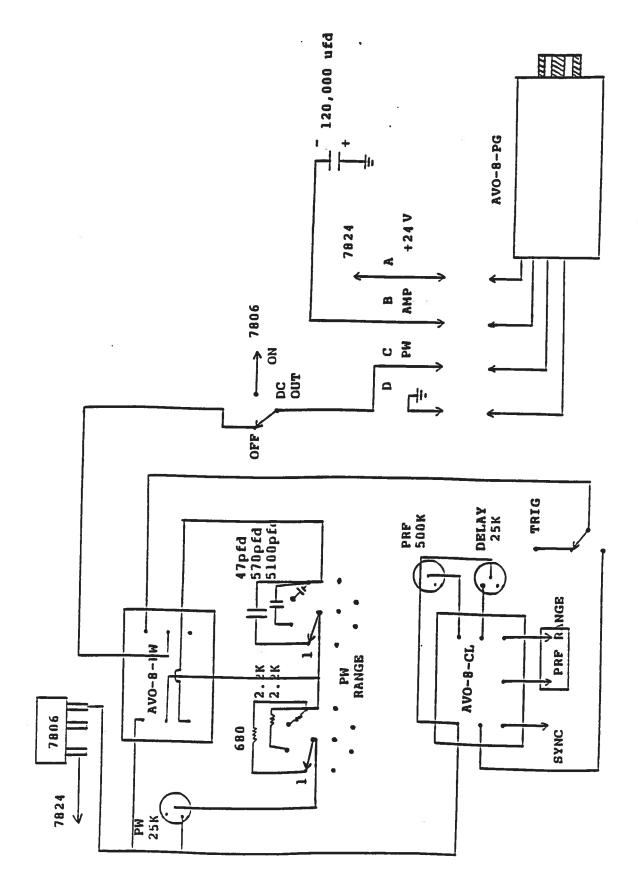

FIG. 1: PULSE GENERATOR TEST ARRANGEMENT

### **GENERAL OPERATING INSTRUCTIONS**

- 1) The equipment should be connected in the general fashion shown above. Since the AVO unit provides an output pulse rise time as low as 0.1 us a fast oscilloscope (at least 50 MHz) should be used to display the waveform.

- The user supplied lab power supply attaches to the -PG output module via the red and black SUPERCON connectors which are supplied. The positive terminal of the power supply is to be connected to the RED SUPERCON connector on the -PG module. The negative terminal on the lab power supply is to be connected to ground and to the BLACK SUPERCON connector on the -PG module.

- The gray cable from the -PG module must be connected to the mainframe rear panel RS-232 style connector.

- The trig output channel provides TTL level signals. To avoid overdriving the TRIG input channel of some scopes, a 30 dB attenuator should be placed at the input to the scope trigger channel. The TRIG output precedes the main output when the front panel ADVANCE-DELAY switch is in the ADVANCE position. The TRIG output lags the main output when the switch is in the DELAY position.

- 5) To obtain a stable output display the PW and PRF controls on the front panel should be set mid-range. The front panel INT-EXT-MAN-DC switch should be in the INT position. The DELAY controls and the scope triggering controls are then adjusted to obtain a stable output. The scope may then be used to set the desired PRF by rotating the PRF controls.

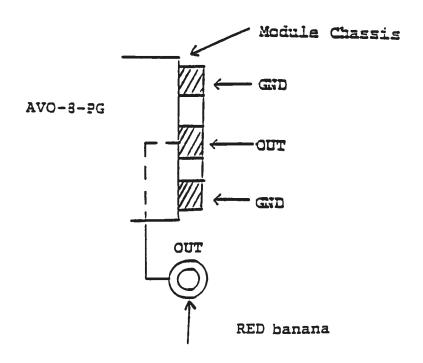

- The output terminals of the pulse generator module consists of a short length of microstrip transmission line protruding from the module chassis. The OUT terminal is the center conductor which is bounded on both sides by the ground plane (see below). Note that the "OUT" red banana terminal is in parallel with the microstrip center conductor and so may also be used as the output terminal. Note that the monitor function works only with banana terminals (and not with the microstrip terminals).

The load should be connected between the OUT and GND terminals using very short leads (≤ 2.0 cm).

Take care to insure that during soldering the OUT conductor is not shorted to the chassis. Also, use minimal heat when soldering.

- 7) When the PW MODE switch is in the INT position, the output pulse width is controlled by the 4 position range switch and one turn fine control. To voltage control the output pulse width within each range, set the rear panel switch in the EXT position and apply 0 to +10 Volts between terminal A and ground ( $R_{IN} \ge 10$ K). (option). (See (9) for PW control when the PW MODE switch is in the EXT position).

- 8) The output amplitude is controlled by the amplitude of the DC potential supplied to the SUPERCON connectors on the PG module.

- 9) An external clock may be used to control the output PRF of the unit by setting the front panel INT-EXT-MAN-DC switch in the EXT position and applying a 50 ns (or wider) TTL level pulse to the TRIG BNC connector input. The external clock may also be used to control the output pulse width by setting the PW mode switch in the EXT position (in this case, PW<sub>OUT</sub> = PW<sub>IN</sub>).

- 10) The AVO-8B is designed to supply up to 100 Amperes peak to a maximum load voltage of 20 Volts. Factory tests are conducted with a 0.2 Ohm load capable of dissipating at least 2000 Watts. Higher load resistance values may be used but the input voltage must be limited to 20 Volts or less. Note that the unit may fail if the average output current exceeds 100 Amp.

- 11) Model AVO-8B will operate with a duty cycle at least as high as 85% when the pulse width is controlled by the front panel Pulse Width and Pulse Width Range controls. A duty cycle of 100% is obtained by setting the pulse width mode switch in the DC position. In this position the PW controls are no longer active. In this position the load voltage will be about 1.0 Volts less than the applied DC voltage for a load current of 100 Amperes. Note that the average output current must never exceed 100 Amp.

- 12) Model AVO-8B-C includes a high voltage protection circuit which sounds a loud audible alarm if the applied DC voltage exceeds ≈ +25 VDC. The output stages of the unit will not trigger while the alarm is sounding. The unit also includes a temperature limit circuit which sounds an audible alarm if the temperature of the output stage switching elements exceeds +35°C.

- 13) The unit can be converted from 110 to 220V 50-60 Hz operation by adjusting the voltage selector card in the rear panel fused voltage selector cable connector assembly.

- 14) The rear panel monitor output BNC (M) provides an output voltage which is proportional to the current flowing through the banana output terminals.

For a monitor load resistance of 50 Ohms:

250mV ≈ 100 Amps

For a monitor load resistance of ≥ 1 K:

500 mV ≈ 100 Amps

Note that the monitor function is not connected to the microstrip output terminals (option).

15) If application assistance is required:

Tel: (613) 226-5772 Fax: (613) 226-2802

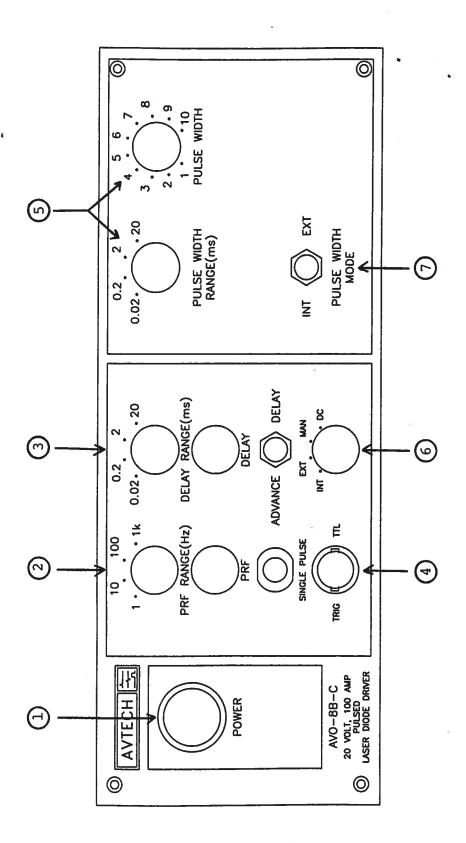

Fig. 2: FRONT PANEL CONTROLS

### **FRONT PANEL CONTROLS**

- (1) <u>ON-OFF Switch</u>. Applies basic prime power to all stages.

- (2) PRF Control. Varies PRF from 10 Hz to 5 kHz as follows:

Range 1 0.1 Hz to 1 Hz

Range 2 1 Hz to 10 Hz

Range 3 10 Hz to 0.1 kHz

Range 4 0.1 kHz to 1 kHz

(3) <u>DELAY Control</u>. Controls the relative delay between the reference output pulse provided at the TRIG output (4) and the -PG output. This delay is variable as follows:

Range 1 2 us to 20 us Range 2 20 us to 200 us Range 3 200 us to 2 ms Range 4 2 ms to 20 ms

The TRIG output precedes the main output when the ADVANCE-DELAY switch is in the ADVANCE position and lags when the switch is in the DELAY position.

- (4) TRIG Output. This output is used to trigger the scope time base. The output is a TTL level 100 ns (approx.) pulse capable of driving a fifty Ohm load.

- (5) <u>PW Control</u>. A one turn control and four position range switch which varies the output pulse width as follows (when the PW MODE switch is in the INT mode):

Range 1 2.0 us to 20 us Range 2 20 us to 200 us Range 3 200 us to 2 ms Range 4 2 ms to 20 ms

(6) EXT-INT Control. With this toggle switch in the INT position, the PRF of the AVO unit is controlled via an internal clock which in turn is controlled by the PRF controls. With the toggle switch in the EXT position, the AVO unit requires a 50 ns (or wider) level pulse applied at the TRIG input in order to trigger the output stages. In addition, in this mode, the scope time base must be triggered by the external trigger source. For single pulse operation, place the switch in the MAN position and push the single pulse button. For DC operation (i.e. 100% duty cycle) place the switch in the DC position.

(7) PW MODE. With the MODE switch in the INT position the PW is controlled by the front panel controls whether the unit is triggered internally or externally. When the switch is in the EXT position, the PW is controlled by the TTL PW applied externally to the TRIG input. Model AVO-8B-C will operate with a duty cycle at least as high as 85% when the PW MODE switch is in the INT position and the pulse is controlled by the front panel Pulse Width and Pulse Width Range controls. A duty cycle of 100% is obtained by setting the INT-EXT-MAN-DC switch in the DC position. In this position the PW controls are no longer active. In this position the load voltage will be about 1.5 Volts less than the applied DC voltage for a load current of 100 Amperes.

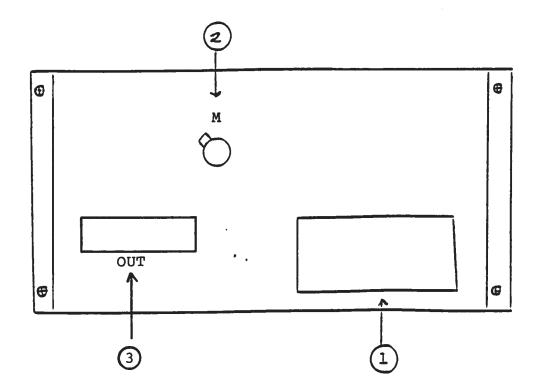

FIG. 3: BACK PANEL CONTROLS

## **BACK PANEL CONTROLS**

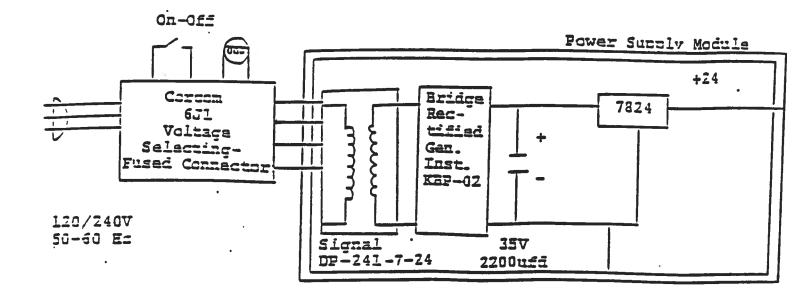

- (1) <u>FUSED CONNECTOR, VOLTAGE SELECTOR</u>. The detachable power cord is connected at this point. In addition, the removable cord is adjusted to select the desired input operating voltage. The unit also contains the main power fuse (0.50 A SB).

- (2) <u>M OUT</u>. BNC connector provides output voltage which is proportional to load current through the banana output terminals as follows:

Monitor load resistance = 50 Ohm:

250 mV ≈ 100 Amps

Monitor load resistance ≥ 1 K:

500 mV ≈ 100 Amps

(3) OUT. The gray RS-232 style cable from the output module connects to this connector.

# AVO-8-C BLOCK DIAGRAM

FIG. 4: SYSTEM BLOCK DIAGRAM

July 23/98

in Word

Edition C

AVO-8B-C (EDC). DOC