# AVTECH ELECTROSYSTEMS LTD.

NANOSECOND WAVEFORM ELECTRONICS ENGINEERING - MANUFACTURING

> BOX 5120. STN. "F" OTTAWA. ONTARIO CANADA K2C 3H4 TEL: (613) 226-5772 FAX: (613) 226-2802 TELEX: 053-4591

P.O. BOX 265 OGDENSBURG NEW YORK 13669 (315) 472-5270

1

INSTRUCTIONS

MODEL AVR-EB2-C-MOTA PULSE GENERATOR

S.N.:

#### WARRANTY

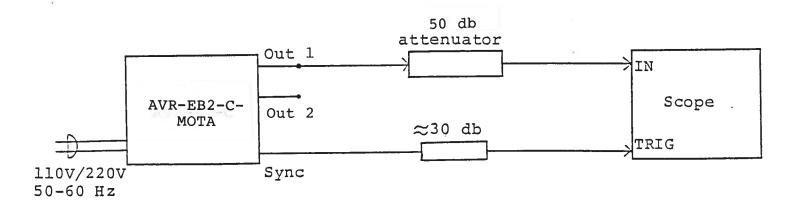

Avtech Electrosystems Ltd. warrants products of its manufacture to be free from defects in material and workmanship under conditions of normal use. If, within one year after delivery to the original owner, and after prepaid return by the original owner, this Avtech product is found to be defective, Avtech shall at its option repair or replace said defective item. This warranty does not apply to units which have been dissembled, modified or subjected to conditions exceeding the applicable specifications or ratings. This warranty is the extent of the obligation or liability assumed by Avtech with respect to this product and no other warranty or guarantee is either expressed or implied. Fig. 1

.

### PULSE GENERATOR TEST ARRANGEMENT

:

#### Notes:

- The bandwidth capability of components and instruments used to display the pulse generator output signal (attenuators, cables, connectors, etc.) should exceed 1.0 GHz.

- 2) The use of 50 db attenuator at the scope vertical input channel will insure a peak input signal to the scope of less than one volt (necessary only if sampling scope used). If a high impedance real time scope is used, the pulse generator should be terminated using a shunt 50 ohm resistor.

- 3) The sync output channel provides TTL level signals. To avoid overdriving the TRIG input channel of some scopes, a 30 db attenuator should be placed at the input to the scope trigger channel. The SYNC output precedes the main output when the front panel LEAD-LAG switch is in the LEAD position. The SYNC output lags the main output when the switch is in the LAG position.

- 4) To obtain a stable output display the PW and PRF controls on the front panel should be set mid-range while the front panel PRF RANGE switch may be in either range. The front panel TRIG toggle switch should be in the INT position. The DELAY controls and the scope triggering controls are then adjusted to obtain a stable output. The scope may then be used to set the desired PRF by rotating the PRF control and by means of the PRF RANGE switch.

- 5) The output pulse width for Channels 1 and 2 is controlled by means of the front panel ten turn PW controls. The controls should be adjusted using an oscilloscope.

- 6) The output pulse amplitude for Channel 1 and Channel 2 is controlled by means of the front panel ten turn AMP controls.

- 7) The delay from the leading edge of the output from Channel 1 to leading edge of the output of Channel 2 is variable from 0 to 5.0 usec using the ten turn DELAY 1-2 control. Channel 1 output (leading edge) always lags the Channel 2 leading edge output.

- 8) An external clock may be used to control the output PRF of the AVR unit by setting the front panel TRIG toggle switch in the EXT position and applying a 0.2 usec (approx.) TTL level pulse to the SYNC BNC connector input. For operation in this mode, the scope time base must also be triggered by the external clock rather than from the SYNC output.

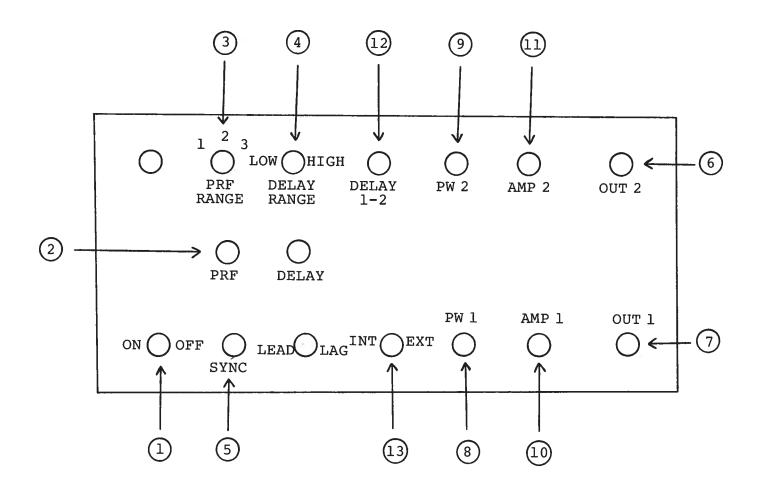

(1) ON-OFF Switch. Applies basic prime power to all stages.

(2) <u>PRF Control</u>. Controls PRF as follows:

(3)

Range 1

20

Hz

to 200

Hz

Range 2

200

Hz

to 2

KHz

Range 3

2

KHz

to 20

KHz

- (4) <u>DELAY Control</u>. Controls the relative delay between the reference output pulse provided at the SYNC output (5) and the Channel 2 output (6). This delay is variable over the range of 0 to about 1.0 usec (LOW) and 1.0 to 5.0 usec (HIGH). The TRIG output precedes the main output when the LEAD-LAG switch is in the LEAD position and lags when the switch is in the LAG position.

- (5) <u>SYNC Output</u>. This output is used to trigger the scope time base. The output is a TTL level 100 nsec (approx.) pulse capable of driving a fifty ohm load. The relative delay between the SYNC output and Channel 2 output is variable from 0 to ±5.0 usec using the DELAY controls.

- (6) <u>OUT 2 Connector</u>. BNC connector provides output to a fifty ohm load (0 to +50 volts, 0.1 to 5.0 usec).

- (7) <u>OUT 1 Connector</u>. BNC connector provides output to a fifty ohm load (0 to -50 volts, 20 to 200 nsec).

- (8) <u>PW Control</u>. Ten turn controls which varies the output(9) pulse width.

- (10) <u>AMP Control</u>. Ten turn controls which varies the output(11) pulse amplitude.

- (12) <u>DELAY 1-2 Control</u>. The delay from the leading edge of the output from Channel 1 to leading edge of the output of Channel 2 is variable from 0 to 5.0 usec using the ten turn DELAY 1-2 control. Channel 1 output (leading edge) always lags the Channel 2 leading edge output.

- (13) <u>EXT-INT Control</u>. With this toggle switch in the INT position, the PRF of the AVR unit is controlled via an internal clock which in turn is controlled by the PRF controls. With the toggle switch in the EXT position, the AVR unit requires a 0.2 usec TTL level pulse applied at the SYNC input in order to trigger the output stages. In addition, in this mode, the scope time base must be triggered by the external trigger source.

Fig. 3

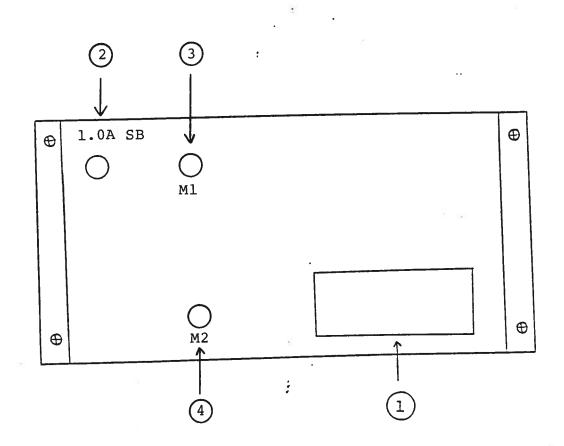

## BACK PANEL CONTROLS

- (1) FUSED CONNECTOR, VOLTAGE SELECTOR. The detachable power cord is connected at this point. In addition, the removable cord is adjusted to select the desired input operating voltage. The unit also contains the main power fuse (0.5A SB).

- (2) <u>1.0A SB</u>. This fuse limits the DC prime power supplied to the output stage and will blow in the case of severe overloading.

- (3) <u>MONITOR Output (M1)</u>. Provides an attenuated (x10) coincident replica (to 50 ohms) of Channel 1 output.

- (4) <u>MONITOR Output (M2)</u>. Provides an attenuated (x10) coincident replica (to 50 ohms) of Channel 2 output.

Fig. 4

AVR-EB2-C-MOTA

e.

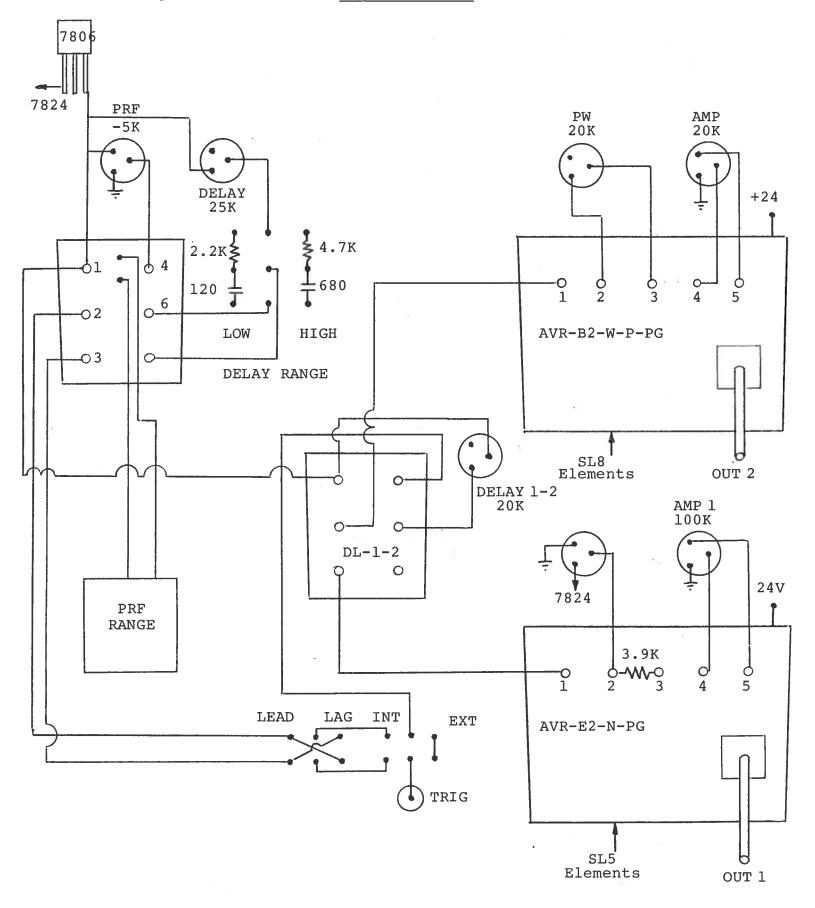

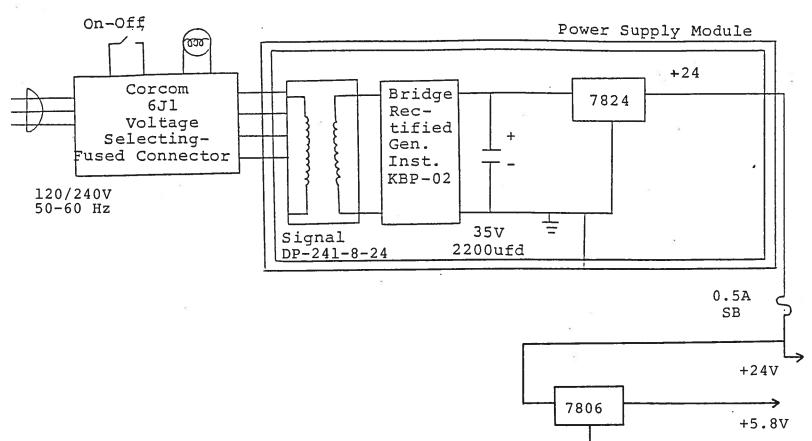

## SYSTEM BLOCK DIAGRAM

Fig. 5

1

#### SYSTEM DESCRIPTION AND REPAIR PROCEDURE

The AVR-EB2-C consists of the following basic modules:

- 1) AVR-B2-W-P-PG pulse generator module

- 2) AVR-E2-N-PG pulse generator module

- 3) AVR-EB2-CL clock module

- 4) AVR-EB2-DL-12 delay module

- 5) +24V power supply board

The modules are interconnected as shown in Fig. 4. The clock module controls the output PRF and the relative delay between the Channel 2 output and the SYNC outputs. The delay module controls the delay between Channel 1 and Channel 2 leading edge outputs. The PG pulse generator modules generate the output pulses. In the event of an instrument malfunction, it is most likely that the rear panel 1.0 SB fuse or some of the output switching elements (SL8, Channel 2; SL5, Channel 1) may have failed due to an output short circuit condition or to a high duty cycle condition. The switching elements may be accessed by removing the cover plates on the bottom side of the instrument. NOTE: First turn off the prime power. The elements may be removed from their sockets by means of a needle nosed pliers. The SL8 and SL5 are selected VMOS power transistors in a TO 202 package and may be checked on a curve tracer. If defective, replacement units should be ordered directly from Avtech. When replacing the SL8 or SL5 switching elements, take care to insure that the short lead (of the three leads) is adjacent to the black dot on the chassis. If the switching elements are not defective, then the four Phillips screws on the back panel should be removed. The top cover may then be slid off and operation of the clock and power supply modules should be checked. The clock module is functioning properly if:

- a) 0.1 usec TTL level outputs are observed at pins 2 and 3.b) The PRF of the outputs can be varied over the range of

- 0.1 Hz to 20 KHz using the PRF and PRF RANGE controls.

- c) The relative delay between the pin 2 and 3 outputs can be varied by at least <u>+</u>5 usec by the DELAY controls.

The sealed clock module must be returned to Avtech for repair or replacement if the above conditions are not observed. The power supply board generates +24V DC to power the other modules. If the voltage is less than +24V, turn off the prime power and unsolder the lead from the 7824 regulator chip on the power supply board. Solder a 100 ohm 5 watt resistor to the 7824 output to ground and turn on the prime power. A voltage of +24 volts should be read. If the voltage is less then the power supply board is defective and should be repaired or replaced.

### AVTECH ELECTROSYSTEMS LTD.

NANOSECOND WAVEFORM ELECTRONICS ENGINEERING – MANUFACTURING

P.O. BOX 265 OGDENSBURG NEW YORK 13669 (315) 472-5270

BOX 5120. STN. "F" OTTAWA, ONTARIO CANADA K2C 3H4 TEL: (613) 226-5772 FAX: (613) 226-2802 TELEX: 053-4591

February 5, 1990.

Luis Reynoso Motorola Inc. P.O. Box 2953 Phoenix, AZ 85062-2953

Dear Luis:

With reference to our recent series of telephone conversations, I am pleased to offer a price and delivery quotation for a special purpose pulse generator suitable for your 1N4148 and 1N4150  $T_{RR}$  and  $T_{FR}$  tests:

Model designation:

Function:

AVR-EB2-MOTA-C.

This model comprises 2 pulse generators (No. 1 and No. 2) in one mainframe which are specifically configured and timed to perform the following tests:

4031.1 Test Condition B (1N4150  $T_{RR}$ ) See Fig. 1.

4031.1 Test Condition B (1N4148  $T_{\rm RR})$  See Fig. 2.

4026.2 (1N4148 T<sub>FR</sub>) See Fig. 3.

The 2 channels may be used separately or together to perform a wide variety of other  $T_{\rm RR}$  tests.

Channel 1

#### Channel 2

Output amplitude: (to 50 ohm) 0 to -50 volts (ten turn locking dial control). 0 to +50 volts (ten turn locking dial control).

Channel 1 Channel 2 20 to 200 nsec 0.1 to 5.0 usec Output pulse width: (ten turn locking (ten turn locking dial control). dial control). Rise, fall time:  $\leq 0.5$  nsec.  $\leq$  5 nsec. 50 ohms. 2 ohms. Source impedance: 20 Hz to 20 KHz. PRF: Share common clock. 3 position range switch and one turn fine control. TTL, 100 nsec, will drive 50 ohms. Sync out: Delay: 0 to +5 usec, 2 position range switch and one turn fine control. (Channel 2 out and to sync out) Delay: 0 to 5 usec via ten turn locking dial (Channel 1 leading control. edge out to Channel 2 leading edge out) <100 nsec. Propagation delay: (EXT trigger in to Channel 2 out) TTL, PW > 50 nsec. External trigger: BNC. Connectors: 4" x 12" x 16". Chassis size: 120/240 V, 50-60 Hz. Prime power: \$4,990.00 US each, Price: FOB Destination. Delivery: 60-90 days ARO. 1 year standard Avtech warranty. Warranty: 2% 10, Net 30 days. Terms: Available options: A) -EA option: 0 to +10 volts applied to rear panel controls output amplitudes when front panel controls disabled by means of rear panel two

position switches.

(add \$835.00 US and -EA suffix).

Available options: (cont'd)

B) -EW option:

0 to +10 volts applied to rear panel controls output pulse widths when front panel controls disabled by means of rear panel two position switches. (add \$835.00 US and -EW suffix).

- C) -M option: Two rear panel monitor outputs provide attenuated (x10) coincident replicas of outputs. (add \$354.00 US and -M suffix).

- D) AVX-1 inverting transformer: May be used to invert output of Channel 1 to provide positive 0.5 nsec rise time pulse for 4026 test. \$267.00 US.

- E) AVX-BP-2 scope probe: Place at input of 50 ohm scope to provide 500 ohms input impedance as detector for 4026 test. \$341.00 US.

Thank you for your interest in our products. Please call me again if you require any additional information or modifications to the above quotation.

Yours truly,

Walter J. Chudobiak Chief Engineer

WJC:pr Encl. Fig. 1-4

M 80 The ( Mickos mul wellaro) CONFR JUND for LOR WIDE BAND (ruain) ~= S= 2 . MI EROSJXIP Tome 1c21 20 20 ×21 K = 100 = R+50. 7/1/ SR USUS - SUPPLIND 123.7 Ś X ar 4 10 aditted pro Dur Enou after 1000 50 2 = K x-40 00-15 AW V 124150 JAR DECAY 1-2 AUR-232-motos SXC Out 2 12100 00 Ŋ ou prut AND 50 SHOULD NOT 13000 × 1000 /20 C, DURARS M 20 RISE TIME OF CHANNER 2 2.v

Yor TET ンシュ ッシン 7  $\Lambda$ 3 1/ しょう 10001 5 クセン JU SU 2. **4** 7 3-6 110 < 22016 A2016 -300 1200 aur 2 STAC +20V

Ą REST CONDI DON tes 31.1 Jez 14/48 Per, Mento

06

22

• / /

- M