NANOSECOND WAVEFORM ELECTRONICS ENGINEERING - MANUFACTURING

P.O. BOX 265 OGDENSBURG NEW YORK 13669 (315) 472-5270 BOX 5120. STN. "F" OTTAWA. ONTARIO CANADA K2C 3H4 TEL: (613) 226-5772 FAX: (613) 226-2802

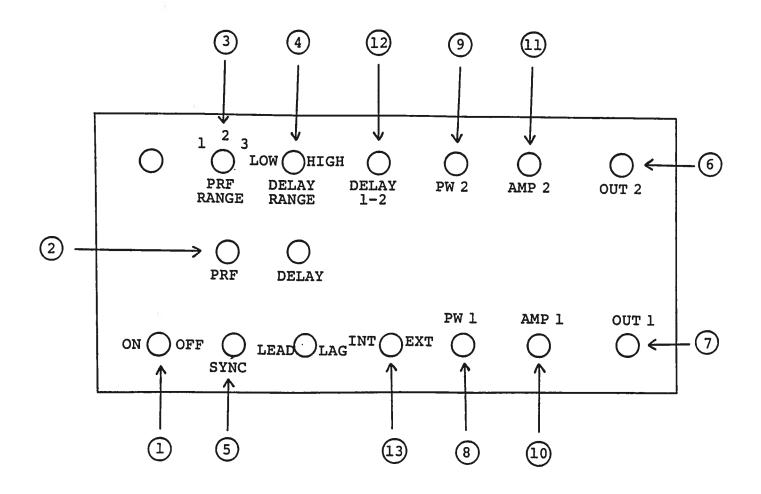

## AVR-EB3-C

General Instructions For Performing T<sub>BB</sub> Measurement, Method 4031.1, Test Condition B (For 1N4150, 1N4148 and 1N5809)

### 1N4150

- Turn both AMP controls on AVR-EB3-C to minimum (see Fig. 1).

- 2) Set PW 1 control to about 0.1 (i.e.  $\gtrsim$  100 ns) and PW 2 control to about 2.0 ( $\gtrsim$ 1.0 us).

- 3) Set DELAY 1-2 on about 1.0.

- 4) Set PRF in Range 3 and PRF one turn control in mid-range ( $\therefore$  PRF  $\approx$  3 KHz).

- 5) Set DELAY in LOW, LAG.

- 6) Connect to diode test jig as shown in Fig. 1A. Note the use of 6 db attenuator pads. CAUTION: Channel 1 of the pulse generator provides a rise time of  $\ll$  1.0 ns. Consequently, the user supplied diode test jig must be extremely broad band or the pulse rise time will be degraded and severe ringing will be observed. It is that the test be constructed recommended jiq on microstrip employing high quality connectors (eg. SMA), microwave capacitors and resistors and that the diode lead lengths be less than 0.2 cm.

- 7) Set scope time base on 50 ns/cm range and vertical to 100 mV/cm.

- 8) Increase AMP 2 to near maximum to obtain display shown in Fig. 2 (adjust DELAY and scope set-up to center waveform display on CRT). With 40 db attenuation on the test jig, the scope reads 10 volts per div (or 200 mA per div). Therefore, set to 2 div to obtain  $I_F = 400$ mA. Note that the coupling of OUT 2 to OUT 1 results in the increase of the rise time of OUT 2 to more than 5 ns. This is due entirely to  $C_P$  in the test jig. For

this reason,  $C_B$  should be limited to 1000 pfd. Note that with OUT 1 disconnected, the fast rise time waveform shown in Fig. 2A is obtained.

- 9) Increase AMP 1 to near maximum to obtain display shown in Fig. 3 (200 mA/div).

- 10) Set scope time base on 5 or 1 ns/div to obtain display shown in Fig. 3A and/or Fig. 3B (adjust DELAY to center on CRT). Note that the leading spike (and ripple) on the  $I_R$  waveform are primarily due to the extremely short rise time of OUT 1 and the parasitic reaction of the test jig. These effects can only be reduced by using a longer rise time.

- 11) Adjust AMP 1 and AMP 2 as desired to obtain final values for  $I_F$  and  $I_R$ . Note that if  $I_F$  is increased then  $I_R$ will decrease (since pulse generators are crossconnected). It is therefore necessary to increase the AMP 1 setting to return  $I_R$  to the original value.

- 12) The DELAY 1-2 control may be adjusted to re-position the leading edge of the  $I_R$  waveform with respect to the leading edge of the  $I_F$  waveform but note that provided DELAY 1-2 is more than about 100 ns, the  $T_{RR}$  reading is quite independent of the DELAY 1-2. Consequently, PW 2 should be limited to less than 1 us and DELAY 1-2 should be in the range of 0.2 to about 0.8 us.

- For additional assistance, call (613) 226-5772.

### 1N4148

- 1) Specifications for the 1N4148 call for  $I_R$ ,  $I_F$  of 10 mA. It is recommended that 16 db attenuation be placed on OUT 1 and OUT 2 and that 20 db replace 40 db in the test jig. For additional instructions see 1N4150 procedure.

- If further assistance or information is required, call (613) 226-5772.

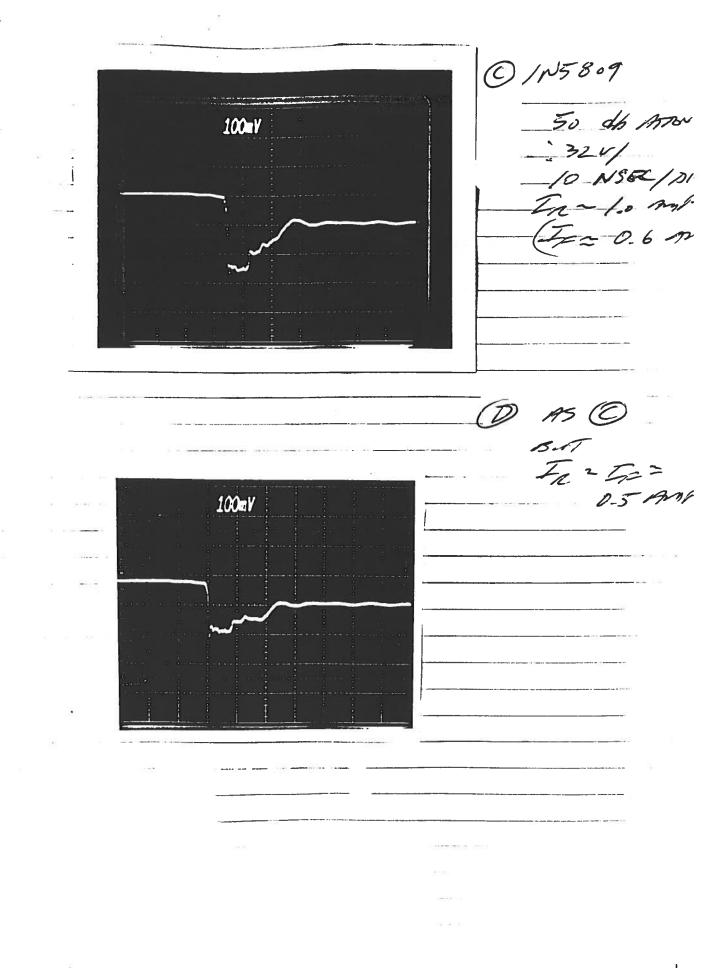

#### 1N5809

- Procedure as for 1N4150 but the input attenuation should be reduced to zero and the output attenuation increased to 50 db.

- 2) For additional assistance, call (613) 226-5772.

(1) <u>ON-OFF Switch</u>. Applies basic prime power to all stages.

(2) <u>PRF Control</u>. Controls PRF as follows:

(3)

Range 1

5

Hz

to

50

Hz

Range 2

50

Hz

to

0.5

KHz

Range 3

0.5

KHz

to

5

KHz

- (4) <u>DELAY Control</u>. Controls the relative delay between the reference output pulse provided at the SYNC output (5) and the Channel 2 output (6). This delay is variable over the range of 0 to about 1.0 usec (LOW) and 1.0 to 5.0 usec (HIGH). The TRIG output precedes the main output when the LEAD-LAG switch is in the LEAD position and lags when the switch is in the LAG position.

- (5) <u>SYNC Output</u>. This output is used to trigger the scope time base. The output is a TTL level 100 nsec (approx.) pulse capable of driving a fifty ohm load. The relative delay between the SYNC output and Channel 2 output is variable from 0 to <u>+</u>5.0 usec using the DELAY controls.

- (6) <u>OUT 2 Connector</u>. BNC connector provides output to a fifty ohm load (0 to +100 volts, 0.1 to 5.0 usec, 1.0 ns rise time).

- (7) <u>OUT 1 Connector</u>. BNC connector provides output to a fifty ohm load (0 to 700 volts, 0.1 to 5.0 us, 5 ns rise time).

- (8) <u>PW Control</u>. Ten turn controls which varies the output(9) pulse width.

- (10) <u>AMP Control</u>. Ten turn controls which varies the output(11) pulse amplitude.

- (12) <u>DELAY 1-2 Control</u>. The delay from the leading edge of the output from Channel 1 to leading edge of the output of Channel 2 is variable from 0 to 5.0 usec using the ten turn DELAY 1-2 control. Channel 1 output (leading edge) always lags the Channel 2 leading edge output.

- (13) <u>EXT-INT Control</u>. With this toggle switch in the INT position, the PRF of the AVR unit is controlled via an internal clock which in turn is controlled by the PRF controls. With the toggle switch in the EXT position, the AVR unit requires a 0.2 usec TTL level pulse applied at the SYNC input in order to trigger the output stages. In addition, in this mode, the scope time base must be triggered by the external trigger source.

USER SUPPLIED MICROSPER TEST SIG. WITH SMA CONNERD. AVR-EB3-C Tet 7604 611 art-54-----(B=1000 PFD 7711-4016 ATTEN 7511 50 0 616 OUT2 TRIG STRC 50 ~ C M3UN Feld 1A: BASIC TRAT SET UP Tem Tan MEASUNDS (IN4150). Rol IN4148 input ATTONUMONS: 16db output ATTENHIMA: 20 db For IN 5809 IN PUT ATTENUATORS - 0 db augur ATTENUAM: 50 db

[124150) . . ig 2 100a.V 50nS AMP 2 NEARE MIL TO OBDAIN I == 400m 4 Es Eig 2A 100 aV AS D BLET OUT 1 50nS DISCONNELTED, NITE KISE TIME IS INCE CATION BY CB IN TBT 116. 100±V 50nS Fig 3 AS @ BUT MAIP INCICONSON NOT MAAX. - 0 SnS Fy 3A AS & BUT 100=V 5 NS /DIV - In ----E-FR 100=V InS NS BA BUT 38 NS IDIU. EF,

AUR-EB3 -C REGULTS 12/4/50 200EV 2rs 400 M.A / DIU 2 rsa / DIU - I x = I= = 400 m/ B IN 4143 100-V 2rs 20 mA/DIV. 2 NSE2/DIV IR= I== 10 mA C16 de Astancimon Mas ON OUTO / ~ 2)

MPRIL 8 91

# AVTECH ELECTROSYSTEMS LTD.

NANOSECOND WAVEFORM ELECTRONICS ENGINEERING - MANUFACTURING

| P.O. BOX 26<br>DGDENSBUR<br>NEW YORK<br>13669<br>315) 472-52 | BOX 5120 STN. "F"<br>OTTAWA, ONTARIO<br>CANADA K2C 3H4<br>(613) 226-5772 |                      |                |

|--------------------------------------------------------------|--------------------------------------------------------------------------|----------------------|----------------|

| Fax No:                                                      | 3853                                                                     | Our Fax No:          | 613-226-2802   |

| То:                                                          | Metrum Viking Labs                                                       | Your Ref No:         |                |

|                                                              |                                                                          | Our Ref:             |                |

| Attn:                                                        | Chuck Cegelski<br>Tel: 415-969-5500                                      | Date:                | April 18, 1991 |

| From:                                                        | Avtech Electrosystems Ltd.                                               | Receivers<br>Fax No: | 415-964-8673   |

| Subject:                                                     | AVR-EB3-C Test Jig                                                       | No. pages<br>faxed:  | 2              |

Following our telephone conversation of April 17, I enclose a rough sketch of a microstrip test for 4031.1 Test Condition B. The 0.1" lines on 1/16" glass epoxy circuit board serve as 50 ohm transmission lines. The lines may be etched or milled (or even "cut and peeled"). At this point I do not have a model number for an acceptable lead socket to hold the diodes (and provide the necessary short lead length).

Rgds

Walter J. Chudobiak Chief Engineer

WJC:pr

APR-633-C MICROSTRIP TEST NIG (4031.1 TOT CONDITION 3) 23" 1000 PFD TO ATTENUM CERAMIC 114 CAPITOM PADSY 5 mainte 300,0E DUT =3" 0.1' K1.5" 0. CLIP SOCKED. 50 often -111 LEARDS BUST E W CARBON COMPOSITION Sog T of MICLOWING ROD RESISTOR BE EXTREMEZY SHORT -(50.2") 16 Doubac -SIDED GLASS-erix 4 CIRCUIT 144 BOMP 2-56 TIP - - " Bensy 90° ANGLE MAGMINE-Septen. SOLDOR TO brand Alance. GLOUND PLANE Drmix1 SPEZTRA MART NO 2052 -0000-00 parent 1) (THERE THERE NON 14?1 Mar

04.25.91

for Metrum / Viking Labs, SN 5861