### AVTECH ELECTROSYSTEMS LTD.

NANOSECOND WAVEFORM ELECTRONICS ENGINEERING - MANUFACTURING

P.O. BOX 265 OGDENSBURG NEW YORK 13669 (315) 472-5270

BOX 5120 STN. "F" OTTAWA, ONTARIO CANADA K2C 3H4 (613) 226-5772 TELEX 053-4591

INSTRUCTIONS

MODEL AVRL-ITT9C PULSE GENERATOR

S.N.:

### WARRANTY

Avtech Electrosystems Ltd. warrants products of its manufacture to be free from defects in material and workmanship under conditions of normal use. If, within one year after delivery to the original owner, and after prepaid return by the original owner, this Avtech product is found to be defective, Avtech shall at its option repair or replace said defective item. This warranty does not apply to units which have been dissembled, modified or subjected to applicable specifications or conditions exceeding the ratings. This warranty is the extent of the obligation or liability assumed by Avtech with respect to this product and no other warranty or guarantee is either expressed or implied.

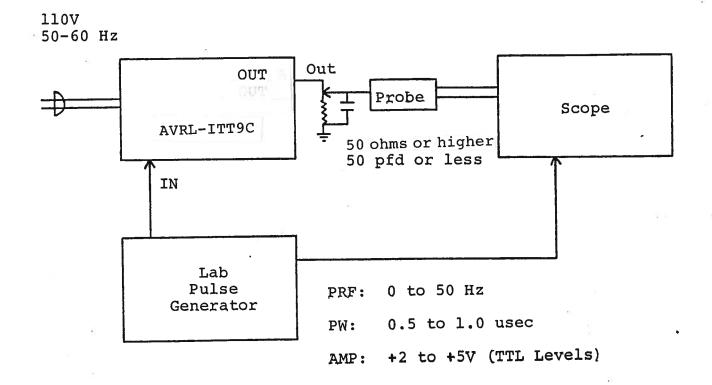

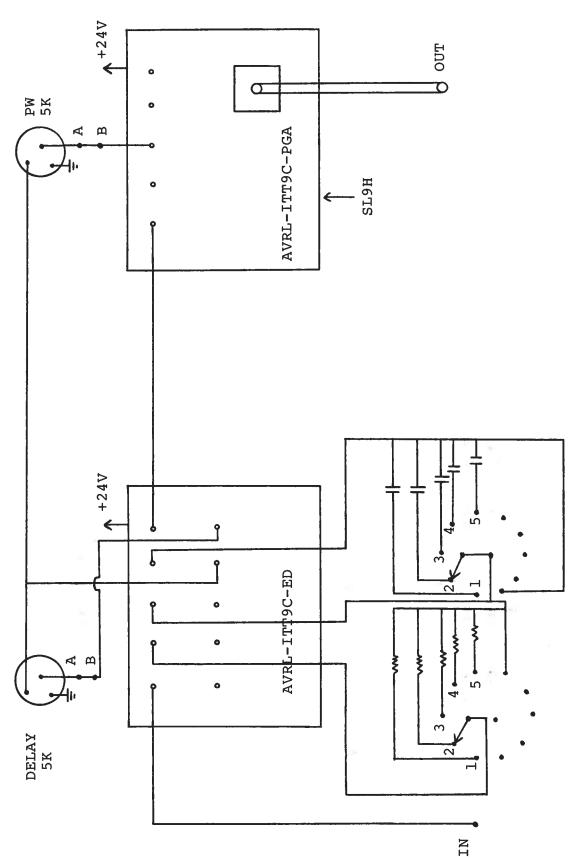

## TEST ARRANGEMENT

#### Notes:

- The equipment should be connected in the general fashion shown above. A scope with a bandwidth of at least 50 MHz should be used to view the outputs.

- The output amplitude is fixed at -200V. Care should be taken to insure that the scope and the load resistor can withstand this high voltage.

- 3) The output pulse width is variable from 20 nsec to 100 nsec using the ten turn front panel control.

- 4) To voltage control the output pulse width, remove the jumper wire between banana plugs A and B on the back panel and apply 0 to +10V to connector B ( $R_{IN} \ge 10K$ ).

- 5) The propagation delay is variable from 1.6 usec to 5.0 msec using the five position delay range switch and the delay fine control (ten turn).

- 6) To voltage control the propagation delay, remove the jumper wire between banana plugs A and B on the back panel and apply 0 to +10V to connector B ( $R_{IN} \gg 10K$ ).

- 7) The output PRF is equal to the input PRF applied to the IN port. Note that the output may fail if above PRF specifications and duty cycle are exceeded or if the load capacitance specification is exceeded.

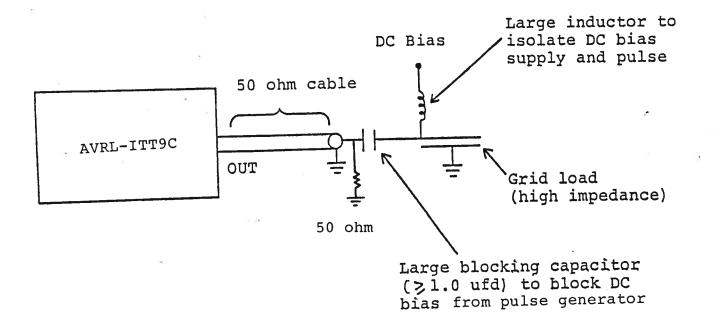

- 8) The unit is designed to operate directly into a 50 ohm load. The unit will operate into a high impedance load (eg. > 1K) but with some increase in output amplitude and overshoot. The following arrangement is recommended when the unit is used to pulse a biased high impedance load:

.

•

, . . **.**

7) The output switching elements (SL9H) will probably fail if the output of the unit is accidentally short-circuited or if the unit is operated at high output pulse width - high PRF combinations. The switching elements are easily replaced following the instructions given in the REPAIR Section. FRONT PANEL CONTROLS

.

67

•

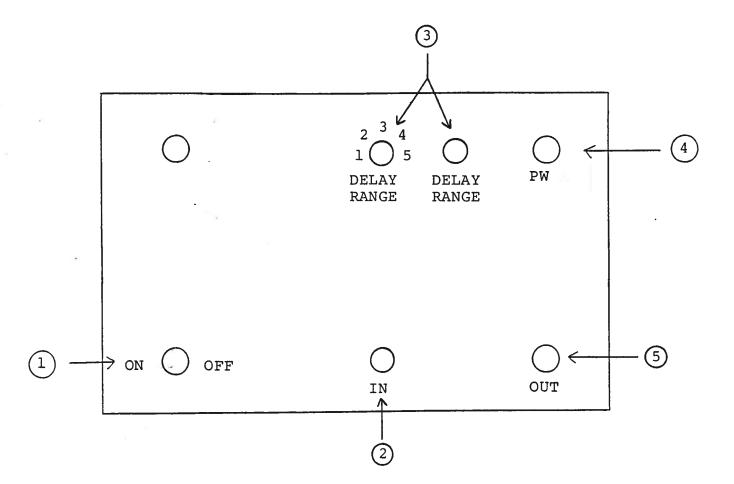

- (1) <u>ON-OFF Switch</u>. Applies prime power to all stages.

- (2) <u>IN</u>. Input trigger applied here (TTL levels, 0.5 to 1.0 usec).

- (3) <u>DELAY RANGE, DELAY FINE</u>. Varies propagation delay from IN to OUT as follows:

RANGE 1:1.6 usec to8 usecRANGE 2:8 usec to40 usecRANGE 3:40 usec to200 usecRANGE 4:200 usec to1 msecRANGE 5:1 msec to5.0 msec

- (4) <u>PW</u>. Ten turn control used to vary output PW from 20 to 100 nsec.

- (5) <u>OUT Connector</u>. BNC connectors used to connect output to load.

## BACK PANEL CONTROLS

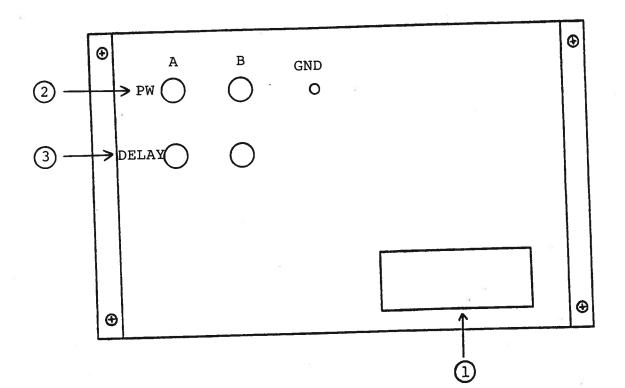

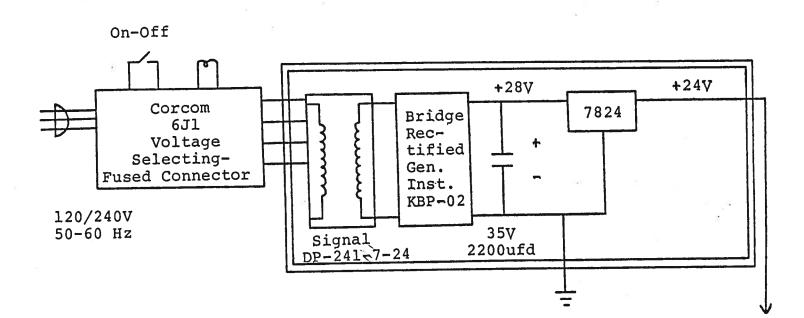

- (1) FUSED CONNECTOR, VOLTAGE SELECTOR. The detachable power cord is connected at this point. In addition, the removable cord is adjusted to select the desired input operating voltage. The unit also contains the main power fuse.

- (2) To voltage control the output pulse width, remove the jumper wire between banana plugs A and B and apply O to +10V to connector B ( $R_{IN} \gg 10K$ ).

- (3) To voltage control the propagation delay, remove the jumper wire between banana plugs A and B and apply O to +10V to connector B ( $R_{IN} \gg 10K$ ).

DELAY RANGE

### +24 VOLT POWER SUPPLY

The AVRL-ITT9C consists of the four standard modules and a power supply board which supplies +24 volts (600 mA max) to the modules. In the event that the unit malfunctions, remove the instrument top cover, thereby exposing the modules. Measure the voltage at the +24 V pin of the PS module. If this voltage is substantially less than +24 volts, unsolder the line connecting the power supply board output and connect a 50 ohm 10 W load to the power supply output. The voltage across this load should be about +24 V DC. If this voltage is substantially less the power supply board is defective and should be repaired or replaced. If the voltage is near +24V then see instructions in preceding section.

## POWER SUPPLY BOARD

### REPAIR PROCEDURE

- 1) WARNING: Before attempting any repairs, note that potentials as high as 200 volts are employed in the chassis structure.

- 2) The pulse generator is constructed from the following subsystems or modules:

- a) Metal chassis

- b) Pulse generator module (AVRL-ITT9C-PGA)

- c) Delay module (AVRL-ITT9C-D)

- d) +24V power supply board

The modules are interconnected as shown in the following diagram.

- 3) If no output is provided then it is most likely that the SL9H switching elements in the output stages have been damaged and should be replaced using the following procedure:

- Turn off prime power and remove cover plate on bottom of instrument (four 2-56 screws).

- ii) By means of a screwdriver, briefly ground the tabs of the two SL9H transistors to discharge the bypass capacitors.

- iii) Extract the old SL9H transistors from their socket by means of needle-nosed pliers.

- iv) Install replacement SL9H transistors and install cover plate.

# Schroff 09.21.87

1 2 2 1 1 2 1 2 1 2 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3 4 1 2 3

-EW

- (a) Model (0, t) in the matrix of a first set of a set of a set of the s

- . A long an-Ato and **effect** on the form in the community of the features in the second s

aran mana - mark arfan matara and af affitheta a ' artalata ''. Tabutat

- אור ביו בא דוריקוא קירואות בוויד באניפיים דויקוא ביו בלו אירי א למיים מיני הל ביישיעי נגאפרים בעירוני בי מיני מיריפאיים

- 3) and the construction of the construction of the first one of the second s